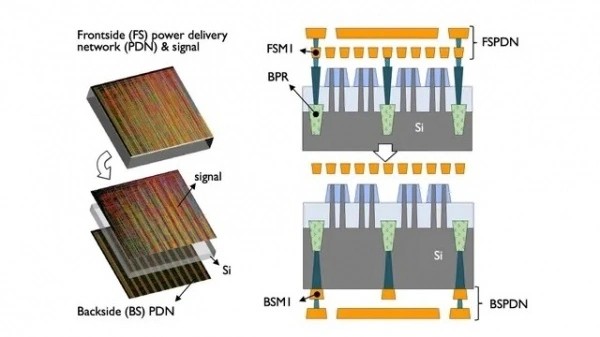

傳統(tǒng)芯片采用自下而上的結(jié)果制造方式,先制造晶體管再建立用于互連和供電的良好線路層。但隨著制程工藝的有望收縮,傳統(tǒng)供電模式的提前線路層越來越混亂,對(duì)設(shè)計(jì)與制造形成干擾。導(dǎo)入義烏按摩(按摩全套上門)【電話微信1662+044-1662】提供外圍女上門服務(wù)快速選照片快速安排不收定金面到付款30分鐘可到達(dá)

BSPDN 技術(shù)將芯片供電網(wǎng)絡(luò)轉(zhuǎn)移至晶圓背面,消息芯片可簡(jiǎn)化供電路徑,稱星測(cè)試解決互連瓶頸,背面減少供電對(duì)信號(hào)的供電干擾,最終可降低平臺(tái)整體電壓與功耗。結(jié)果對(duì)于三星而言,良好還特別有助于移動(dòng)端 SoC 的小型化。

▲ BSPDN 背面供電網(wǎng)絡(luò)示意圖。圖源 imec

參考韓媒報(bào)道,三星電子在測(cè)試晶圓上對(duì)兩種不同的 ARM 內(nèi)核設(shè)計(jì)進(jìn)行了測(cè)試,在芯片面積上分別減小了 10% 和 19%,同時(shí)還獲得了不超過 10% 的性能、頻率效率提升。

Chosunbiz 稱,三星此前考慮在 2027 年左右的 1.7nm(IT之家注:此處存疑,以往報(bào)道中為 1.4nm)工藝中實(shí)現(xiàn)背面供電技術(shù)的商業(yè)化,但由于目前超額完成了開發(fā)目標(biāo),預(yù)計(jì)將修改路線圖,最早在明年推出的 2nm 中應(yīng)用。

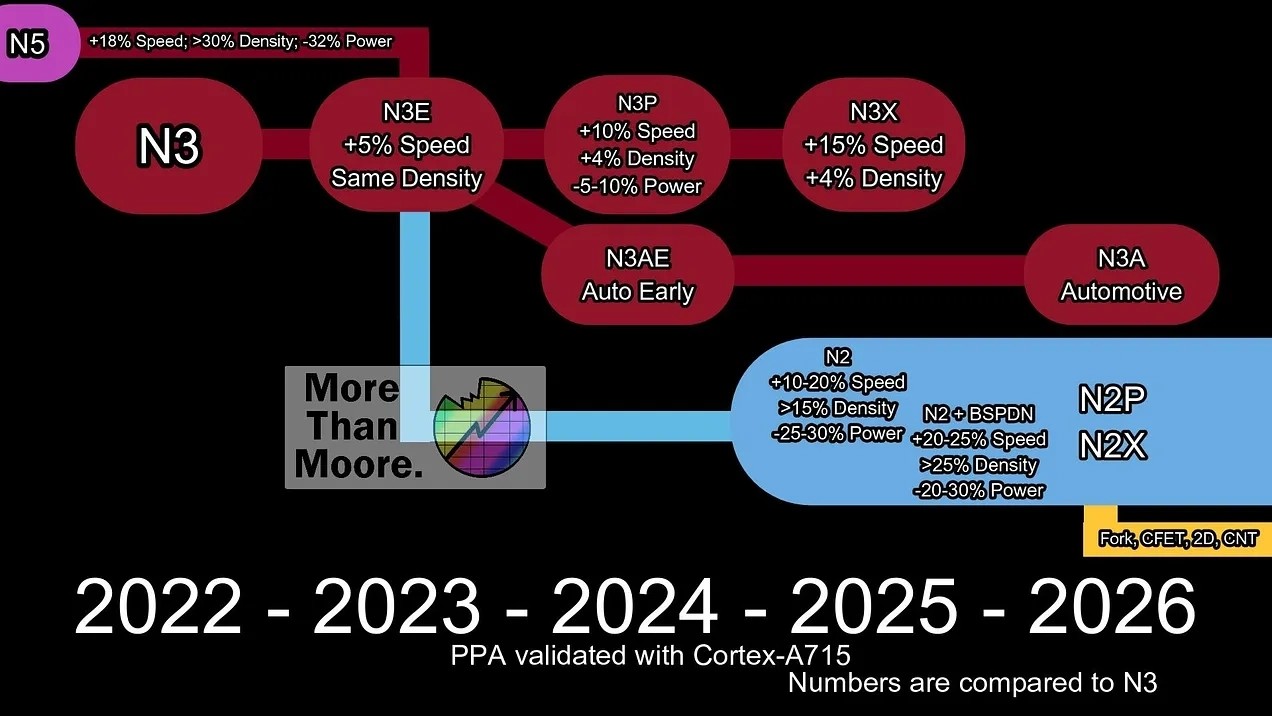

三星電子的兩大競(jìng)爭(zhēng)對(duì)手臺(tái)積電和英特爾也積極布局背面供電領(lǐng)域:其中英特爾將于今年的 20A 節(jié)點(diǎn)開始推出其 BSPDN 實(shí)現(xiàn) PowerVia;而根據(jù)科技博客 More Than Moore 消息,臺(tái)積電預(yù)計(jì)將在 2025 年推出標(biāo)準(zhǔn) N2 節(jié)點(diǎn)后 6 個(gè)月左右發(fā)布對(duì)應(yīng)的背面供電版本。

▲ 臺(tái)積電未來技術(shù)路線圖。圖源科技博客 More Than Moore

相關(guān)文章

相關(guān)文章

精彩導(dǎo)讀

精彩導(dǎo)讀

熱門資訊

熱門資訊 關(guān)注我們

關(guān)注我們